# What future do you want to connect with?

# Programme

24<sup>th</sup> European Microelectronics & Packaging Conference and Exhibition

12 – 14 September 2023 Cambridge, UK

For more information, visit

empc2023.org

**Platinum Sponsor**

Co-sponsored by:

Organised by:

# **CONTENT**

| Welcome                                       | 4  |

|-----------------------------------------------|----|

| Committees                                    | 6  |

| Keynote Speakers                              | 9  |

| Monday, September 11, Programme Overview      | 15 |

| Tuesday, September 12, Programme Overview     |    |

| Wednesday, September 13, Programme Overview   | 31 |

| Thursday, September 14, Programme Overview    | 41 |

| Networking Events                             | 46 |

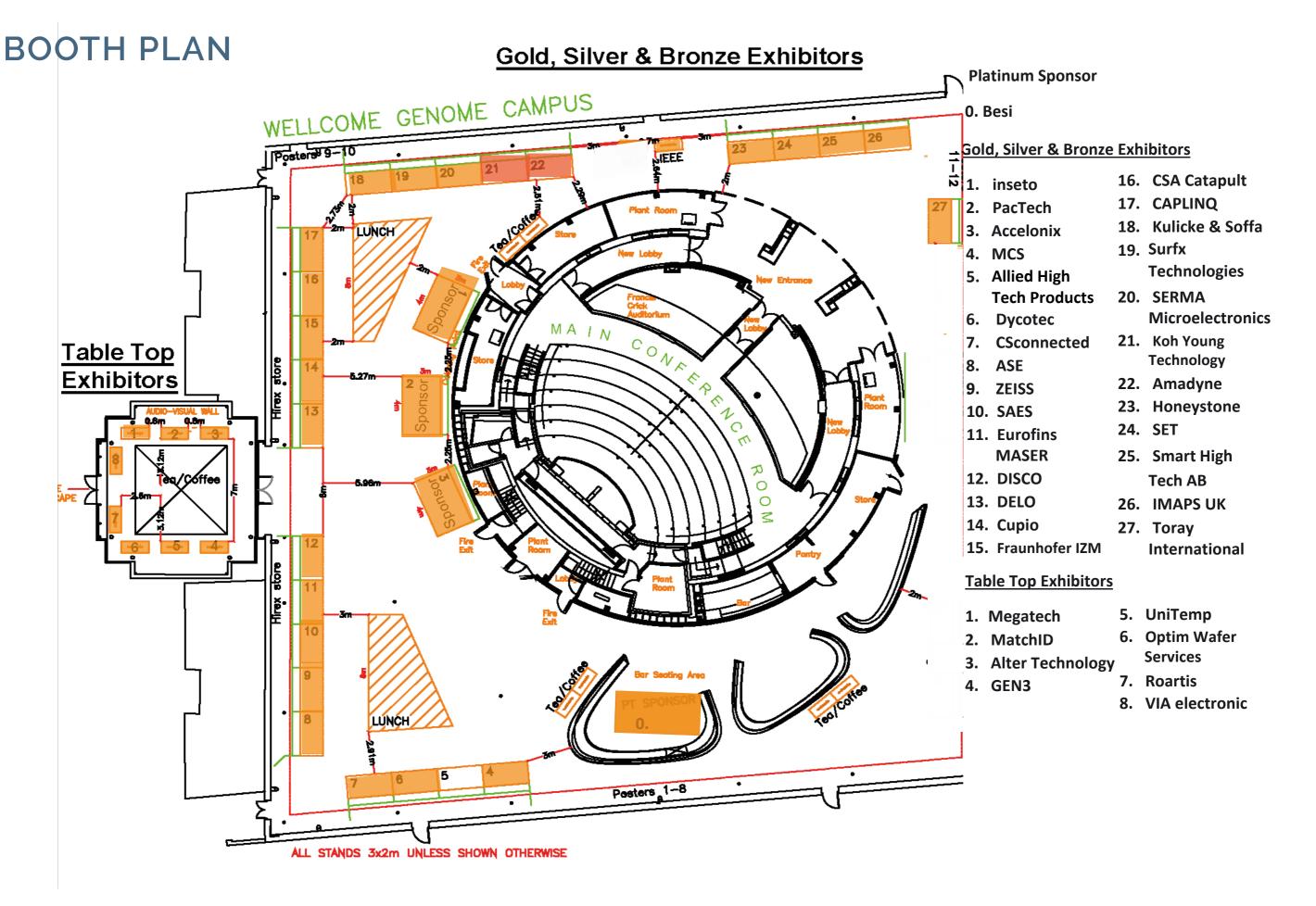

| Exhibitors                                    | 49 |

| Booth Plan                                    | 50 |

| Platinum, Gold and Silver Exhibitors Showcase | 52 |

# **WELCOME TO EMPC 2023**

Welcome to the 24<sup>th</sup> European Microelectronics Packaging Conference being held at the Wellcome Genome Campus (EMPC 2023). This biennial Conference is organised by IMAPS-UK with the support of IMAPS-Europe and is cosponsored by the IEEE – Electronics Packaging Society.

The conference will present the latest developments in the field of microelectronics packaging and interconnection technologies from industrial and R&D organisations located across the world. Over 90 abstracts have been organised

into 20 sessions and posters over the 3 days of the conference, with ample time for attendees to interact with the exhibitors in the integrated venue. The conference welcomes over 250 attendees from the UK, the rest of Europe and around the world.

The five keynote speakers represent leading edge companies, all pushing the boundaries of what can be achieved with microelectronics packaging in a wide range of applications. We are delighted to welcome Chris Scanlon of BESI, Florin Udrea of Cambridge GaN Devices, Ali Murad of Paragraf, Mark Gerber of ASE Group and Feras Alkhalil of Pragmatic Semiconductor to give their perspective of the challenges faced and solutions delivered in this ever more complex world of microelectronics.

In addition to the comprehensive conference programme of presentations and posters, there are many opportunities to meet with the Exhibitors in the co-located space, who represent the breadth of the microelectronics supply chain. We are particularly grateful for the support of the Platinum sponsor, BESI, the three Gold sponsors – Accelonix, Inseto and PacTech and to ASE Group for sponsoring the welcome reception, the conference dinner and the lanyards.

A ceremony is planned at the close of the conference, where we will present the EMPC 2023 Best Paper and Poster Awards and thank all the authors who presented their work.

The welcome reception and conference dinner will be held in Homerton College in Cambridge. You will have the opportunity to make new contacts and meet old friends in the ambience of a modern collegiate dining room and spacious gardens. We hope that you will also have time to visit the city of Cambridge, with its many historic colleges, museums and art galleries.

Finally I express my most sincere gratitude to the Technical Committee and the EMPC 2023 organising team for supporting the conference, reviewing the papers and helping the EMPC conference maintain its high technical and scientific standards.

#### WE WISH YOU AN EXCELLENT EMPC 2023 CONFERENCE.

#### Anne Vanhoestenberghe

and the EMPC2023 organising team

4 | | | | | | |

## SCIENTIFIC COMMITTEE

#### Conference Chair:

Anne Vanhoestenberghe, King's College London, UK

#### **Organising Committee:**

Stephen Riches, IMAPS-UK, UK

Peter Barnwell, IMAPS-UK Trustee, UK

Andrew Holland, RF Module And Optical Design Limited, UK

John Lipp, IMAPS-UK, UK

Eamonn Redmond, Inseto (UK) Ltd, UK

Martin Wickham, National Physical Laboratory, UK

Scott Wood, Accelonix, UK

#### Technical Committee:

Hassan Akhtar Manufacturing Technology Centre, UK

**Rolf Aschenbrenner** Fraunhofer IZM, DE **Peter Barnwell** IMAPS-UK Trustee, UK

Derek Braden Aptiv, UK

Luigi CalligarichELECTRON MEC, ITJayakrishnan ChandrappanCSA Catapult, UK

Norocel Codreanu University POLITEHNICA of Bucharest, RO

Paul Collander IMAPS Nordic, FI Suzanne Costello MCS Ltd, UK

Gerard Cummins University of Birmingham, UK

Giovanni Delrosso VTT Technical Research Center of Finland, FI

Bradford Factor ASE, FR

Attila Géczy Budapest University of Technology and Economics, HU

Andrew Holland RF Module And Optical Design Limited, UK

Szendiuch Ivan Brno University of Technology, CZ

Malgorzata Jacubowska Warsaw University of Technology, PL

Jeff KettleUniversity of Glasgow, UKDavid KingAlter Technology, UK

Olivér Krammer Budapest University of Technology and Economics, HU

John David Lipp IMAPS-UK, UK

Andy Longford PandA Europe, UK

Wendy Luiten WLC, NL

Jens Müller Technische Universität Ilmenau, DE Viorel Nicolau "Dunarea de Jos" University of Galati, RO

Eamonn RedmondInseto (UK) Ltd, UKStephen RichesIMAPS-UK, UKMark ShawSTMicroelectronics, ITCarolyn ShortKLA Corporation, UK

Stoyan Stoyanov University of Greenwich, UK

Tatjana TrajkovicCambridge Microelectronics Ltd, UKSusan TrulliRaytheon Missiles and Defense, MAMartin WickhamNational Physical Laboratory, UK

Scott Wood Accelonix, UK

6

## **KEYNOTE SPEAKERS**

KEYNOTE 1

INTERCONNECTING CHIPLETS

Chris Scanlon, Senior Vice President Technology, BESI Switzerland

#### Abstract

The semiconductor industry is undergoing a shift from traditional transistor scaling to heterogeneous integration (HI) using chiplets. While SoC is becoming infeasible for some applications due to the limitations of Moore's Law, chiplets provide a way to continue system-level scaling through More than Moore. However, chiplet systems can be complex and require a hierarchy of different interconnect types in the same package. The most advanced interconnect technology for chiplets is hybrid bonding, which connects chips directly with Cu-Cu bonds. Die-to-wafer hybrid

bonding has already been in volume production since 2022 for high-performance computing (HPC) applications. However, complete HI systems require other advanced wafer-level assembly processes as well, including TCB, fan-out and bridge die attach, wafer-level flip-chip, and wafer molding. In the near future, photonic chiplets will be introduced, and together these interconnect methods can form a hierarchy of interconnect in complex chiplet systems. In this speech we will explore the opportunities and challenges of chiplet integration for continued system-level scaling. We will discuss the different interconnect technologies used in chiplet systems and the advancements in assembly equipment that enable these high density interconnects. We will also examine the importance of collaboration and standardization in the chiplet ecosystem and how they can enable the rapid development of new products and business models.

#### Biography

Chris Scanlan is Senior Vice President Technology at Besi Switzerland where he is leading advanced technology road map development and technical promotion. Prior to joining Besi he was Vice President of Worldwide Applications Engineering at JCET Group where he was responsible for business development, technical program management and product design. From 2009 to 2019 he was SVP of Product Development at Deca Technologies. Chris was primarily responsible for the development of Deca's portfolio of intellectual property and technology relating to advanced wafer-level manufacturing methods. Chris worked at Amkor Technology for 10 years where he held leadership positions including VPs of Global R&D, Advanced Products and System in Package business units. Chris started his career at Motorola Semiconductor covering manufacturing of high power IGBT modules and transfer of fcCSP technology from R&D to production. He has 70 issued US patents related to semiconductor packaging. He earned his MSc. degree in Materials Engineering from the University of Wisconsin-Milwaukee.

8

#### **KEYNOTE SPEAKERS**

Keynote 2

KEYNOTE: WIDE BANDGAP DEVICES AND MULTI-DIMENSIONAL ARCHITECTURES IN THE NEW ERA OF POWER ELECTRONICS

Professor Florin Udrea, Cambridge GaN Devices, UK

#### Abstract

The power devices field has seen tremendous changes in the last decade. Most of the innovation in the field comes from the emergence of Wide Bandgap semiconductors – and in particular those based on Gallium Nitride and Silicon Carbide. Extensive research is also carried out in single crystal Diamond, Gallium Oxide and Aluminium Nitride materials. The market of power devices has reached ~\$50M with exponential growth in wide bandgap materials reaching CAGRs in excess of 50% in the next 3-5 years.

This talk will cover an exciting range of wide bandgap (WBG) and ultra wide bandgap (UWBG) semiconductor technologies and materials for power devices. The talk will also address the new multi-dimensional architectures to further increase efficiency of power semiconductor devices.

#### **Biography**

Professor Florin Udrea is a professor in semiconductor engineering and head of the High Voltage Microelectronics and Sensors Laboratory at University of Cambridge. He is currently leading a research group in power semiconductor devices and solid-state sensors that has won an international reputation during the last 25 years. Prof. Udrea has published over 500 papers in journals and international conferences and holds over 200 patents in power semiconductor devices and sensors. Prof. Florin Udrea founded five companies, including Cambridge GaN Devices in high voltage GaN technology. For his 'outstanding personal contribution to British Engineering' he has been awarded the Silver Medal from the Royal Academy of Engineering. In 2015 Prof. Florin Udrea was elected a Fellow of Royal Academy of Engineering. In 2018 Prof. Udrea has been awarded several major prizes, including the Mullard medal from the Royal Society. In 2020 he received the Ohmi award as a co-author of the ISPSD paper on Silicon Carbide FInFETs. In 2021 he was awarded the academic entrepreneur of the year in UK by Business Weekly.

#### Keynote 3

# KEYNOTE: THE CHALLENGES OF INTEGRATING GRAPHENE INTO EXISTING PACKAGES

Dr. Ali Murad, Test & Packaging Engineer. Paragraf, UK

#### Abstract

Graphene has been one of the most exciting materials in recent years for a wide variety of industries ranging from electronics, energy, medicine, sensors, and many more. It has been referred to as a wonder material due to its incredible mechanical strength, lightness, flexibility, optical transparency, and impressive semiconductor properties (of both electricity and heat). Paragraf is the first company in the world to mass produce graphene-based electronic devices using standard semiconductor manufacturing processes, has been at the forefront

of this effort. However, there are industrywide challenges related to graphene which Paragraf continues to overcome. Some of the challenges are, getting high-quality uniform contamination-free graphene, managing device integration to graphene, integrating graphene devices to industry standard packaging etc. This talk will focus on discussing these challenges, including how Paragraf is producing high-volume graphene based devices for industry applications. This talk will also focus on the latest development of Paragraf's technology and how Paragraf is using its technology to solve real-world problems like heat detection in EV batteries, brushless motors, and many more. In summary, this talk is aiming to provide an overview of the challenges of integrating graphene into packages and the role Paragraf is playing in advancing the use of graphene in industrial applications.

#### **Biography**

Dr. Ali Murad is a Test and Packaging Engineer at Paragraf Ltd., specializing in nanotechnology and semiconductor packaging. With a distinguished background in the field and experience at Intel Corporation and Nexperia Ltd., Dr. Murad brings extensive industry knowledge and expertise. As a sought-after keynote speaker, he shares valuable insights on the latest advancements and trends in nanotechnology and semiconductor packaging.

#### **KEYNOTE SPEAKERS**

Keynote 4

KEYNOTE: ADVANCED PACKAGING - CHALLENGES THAT ARE DRIVING NEW PACKAGE INNOVATION & ECOSYSTEM NEEDS

Mark Gerber, Sr. Director Engineering and Technical Marketing, ASE Group, USA

#### Abstract

Advanced silicon node challenges, and the drive within industry to find new ways of offering the highest level of performance, are driving many new ways to extend advanced packaging. Many analysts defined advanced packaging as packaging that uses a higher density of interconnect, outside of the traditional wire-bond. This category opens a broad spectrum of packaging solutions that include, Flip Chip, Fan Out Wafer Level Packaging, Hybrid Packaging, System in Package, 2.5D/3D and many sub-categories. As yield enhancement

and performance improvements are driving design considerations, such as heterogeneous and homogenous integration, it is becoming more complex to navigate this plethora of new options and to understand the key trade-offs in selecting the right package solution. Challenges including power delivery signal integrity, multi-physics impacts, IP block interface standards, chiplet manufacturing considerations, warpage and many others are driving the ecosystem to change to meet these new and evolving needs. The traditional 2D mindset for silicon integration in packaging is rapidly changing and a 3D or vertical mindset is becoming a key driver for HPC, AI and is extending into mobile products. In this plenary talk, I will discuss these challenges and also talk about some of the solutions as well as needs from the ecosystem to help enable this new era.

#### **Biography**

Mark is Sr. Director of Engineering and Marketing at ASE (US) Inc., He manages a team that supports customer activities around the world focused on all market segments with package multiple platform focus areas including Flip Chip, Copper Pillar, Advanced RDL and SiP Packaging Technologies. Mark has +20 years of semiconductor packaging experience working for Advanced Semiconductor Engineering-ASE, Texas Instruments, Motorola and Dallas Semiconductor in various areas of design, manufacturing, and assembly with an emphasis on the development of new technologies and processes. Mark has served as general chair for multiple conferences, led multiple committees for IMAPS and IEEE and is currently serving on the IMAPS executive committee as a director. Mark was awarded the IMAPS Fellow title in 2018. He holds a bachelor's degree in mechanical engineering from Texas A&M University, has written +20 papers and holds 38 semiconductor packaging patents.

#### Keynote 5

#### KEYNOTE: REINVENTING ELECTRONICS FOR A SUSTAINABLE WORLD

Dr Feras Alkhalil, Principal Scientist and Director of R&D, Pragmatic Semiconductor, UK

#### Abstract

Tackling challenges associated with the climate crisis, sustainability of food supplies and healthcare inequalities require innovative sustainable approaches. Pragmatic Semiconductor is a world leader in the design, development and manufacture of ultra-low-cost Flexible Integrated Circuits (FlexICs). Pragmatic's FlexICs technology is unique in allowing designers to access extremely agile design cycles, coupled with a low cost and low environmental footprint distributed manufacturing model, this enables sustainable democratised innovation. In this session, we will

present Pragmatic's innovative FlexIC Foundry™, offering novel form-factor integrated circuits, that can be used to create ubiquitous low-cost smart systems. We will also present novel emerging technologies, that we are currently developing, that will enable designers to create even more innovative designs with Pragmatic's FlexIC Foundry.

#### Biography

Dr Feras Alkhalil is the Director of R&D at Pragmatic Semiconductor. Feras has been leading the Research and Development activities at Pragmatic since 2015, responsible for early-stage technology development. Feras has an Electronics Engineering background and received an MSc and Ph.D. from the University of Southampton in Microelectronics System Design and Solid-State Quantum Electronics, respectively. Feras taught Semiconductor Physics at the University of Southampton in Malaysia 2013-2015, holds a visiting fellowship with Durham University since 2017, and has more than 10 patents and is published in over 18 international journals.

# PRE-CONFERENCE DAY

**Pre-Conference Registration**

7:30 pm

# MONDAY, SEPTEMBER 11, 2023

| 8:30 am –<br>6:00 pm | Pre-Registration                                                                                                                              |                                                                                                                                                |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 9:00 am –<br>1:00 pm | SC 1: EVOLUTION OF DIE ATTACH ADHESIVES & ENCAPSULANTS USED IN SEMI-CONDUCTOR PACKAGING Course instructor: Tony Winster, Henkel Ltd., Germany | SC 2: FAN-OUT, CHIPLET DESIGN, AND HETEROGENE- OUS INTEGRATION PACKAGING Course instructor: John H. Lau, Unimicron Technology Corporation, USA |

| 1:30 pm –<br>5:30 pm | SC 3: POWER ELECTRONICS PACKAGING – UNDERSTANDING THE PACKAGING PROCESSES Course instructor: Andy Longford, PandA Europe, UK                  | SC 4: FROM WAFER TO PANEL<br>LEVEL PACKAGING<br>Course instructors: Tanja Braun,<br>Markus Wöhrmann, Fraunhofer<br>IZM, Germany                |

| 6:00 pm -            | Welcome Reception at Homerton College and                                                                                                     |                                                                                                                                                |

14  $\mid$  1

# DAY 1

# TUESDAY, SEPTEMBER 12, 2023

| 8:30 am –<br>8:55 am   | Registration / Networking                                                                                                                              |                                       |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| 8:55 am –<br>9:10 am   | Welcome & Conference Opening Chair: Anne Vanhoestenberghe, King's College London                                                                       |                                       |

| 9:10 am –<br>9:40 am   | KEYNOTE 1: INTERCONNECTING CHIPLETS  Chris Scanlon, Senior Vice President Technology, BESI Switzerland                                                 |                                       |

| 9:45 am –<br>10:45 am  | S 1A: SUBSTRATES:<br>LTCC AND HTCC                                                                                                                     | S 1B: EMBEDDING                       |

| 11:15 am –<br>12:35 pm | S 2A: INTERCONNECT<br>MATERIALS I                                                                                                                      | S 2B: MEMS/SENSORS                    |

| 1:40 pm –<br>2:10 pm   | KEYNOTE 2: WIDE BANDGAP DEVICES AND MULTI-DIMENSIONAL ARCHITECTURES IN THE NEW ERA OF POWER ELECTRONICS  Professor Florin Udrea, Cambridge GaN Devices |                                       |

| 2:15 pm –<br>3:15 pm   | S 3A: SUBSTRATES – THICK FILM AND CU INTERCONNECTS                                                                                                     | S 3B: ADHESIVES AND EN-<br>CAPSULANTS |

| 3:45 pm –<br>5:05 pm   | S 4A: INTERCONNECT<br>MATERIALS II                                                                                                                     | S 4B: MEDICAL                         |

| 5:10 pm –<br>7:00 pm   | Exhibition, Poster, Pizza                                                                                                                              |                                       |

#### 1A: SUBSTRATES: LTCC AND HTCC

#### Session Chair: Peter Barnwell, IMAPS-UK Trustee, UK

→ Location: Main Conference Room

9:45 am – HIGH FREQUENCY BANDWIDTH TRANSITION FOR

10:05 am HTCC HERMETIC PACKAGES

Emad Elrifai EGIDE, France

10:05 am – APPLICATION OF REACTIVE BONDING METHODS ON

10:25 am LTCC SUBSTRATES

Erik Wiss<sup>1</sup>, Alexander Schulz<sup>2</sup>, Adam Yuile<sup>1</sup>, Jens Müller<sup>2</sup>,

Steffen Wiese<sup>1</sup>

<sup>1</sup>Saarland University, Chair of Microintegration and Reliability, Germany; <sup>2</sup>TU Ilmenau, Electronics Technology Group, Germany

10:25 am – LTCC-BASED CERAMIC SUBSTRATES FOR IDENTIFICATION

10:45 am OF TRUSTWORTHY ELECTRONICS

<u>Uwe Krieger<sup>1</sup></u>, Annett Schroeter<sup>1</sup>, Franz Bechtold<sup>1</sup>, Gunter Hagen<sup>2</sup>,

Adrian Goldberg<sup>3</sup>

<sup>1</sup>VIA electronic GmbH, Germany; <sup>2</sup>KMS Technology Center GmbH,

Germany; <sup>3</sup>Fraunhofer Institute for Ceramic Technologies and

Systems IKTS, Germany

10:45 am – Break - Exhibition

11:15 am

## 1B: EMBEDDING

Chairs: Viorel Nicolau, "Dunarea de Jos" University of Galati, Romania

→ Location: Rosalind Franklin Pavilion

9:45 am - CONCEPTS FOR REALIZING HIGH-VOLTAGE POWER MODULES

10:05 am BY EMBEDDING OF SIC SEMICONDUCTORS

Lars Böttcher, Andreas Ostmann, Thomas Löher, Manuel Seckel

Fraunhofer IZM, Germany

10:05 am - CERAMIC EMBEDDING OF SIC-SEMICONDUCTORS USING

10:25 am COFIRING TECHNOLOGY

Steffen Ziesche<sup>1</sup>, Jobin Varghese<sup>1</sup>, Kathrin Reinhardt<sup>1</sup>,

Birgit Manhica<sup>1</sup>, Andreas Schletz<sup>2</sup>

<sup>1</sup>Fraunhofer IKTS, Germany; <sup>2</sup>Fraunhofer IISB, Germany

10:25 am - CHARACTERIZATION OF EMBEDDED AND THINNED RF CHIPS

**10:45 am** Ran Yin<sup>1,2</sup>, Helmuth P. E. Morath<sup>1,3</sup>, Christian Hoyer<sup>3</sup>, Krzysztof

Nieweglowski<sup>1,2</sup>, Karsten Meier<sup>2</sup>, Karlheinz Bock<sup>1,2</sup>

<sup>1</sup>Centre for Tactile Internet with Human-in-the-Loop (CeTI), Germany; <sup>2</sup>Institute of Electronic Packaging Technology, TU Dresden, Germany; <sup>3</sup>Chair of Circuit Design and Network Theory, TU Dresden,

Germany

10:45 am – Break - Exhibition

11:15 am

### 2A: INTERCONNECT MATERIALS I

#### Session Chair: Rolf Aschenbrenner, Fraunhofer IZM, Germany

→ Location: Main Conference Room

DEPOSITION OF FINE-PITCH INDIUM BUMPS ON SINGLE DIE 11:15 am -Andreas Schneider<sup>1</sup>, Navid Ghorbanian<sup>1</sup>, David Burt<sup>2</sup>, James 11:35 am

Hollingham<sup>1</sup>, Paul Booker<sup>1</sup>, Toby G. Brookes<sup>1</sup>, John D. Lipp<sup>1</sup>,

Marcus J. French<sup>1</sup>

<sup>1</sup>STFC-RAL, United Kingdom; <sup>2</sup>Kelvin Nanotechnology Ltd.,

United Kingdom

SILVER BONDING WIRE - AN ALTERNATIVE FOR MECHANICAL 11:35 am -11:55 am

SENSITIVE CHIP CONFIGURATIONS IN AUTOMOTIVE ELECTRO-

**NICS PACKAGING**

Robert Klengel<sup>1</sup>, Sandy Klengel<sup>1</sup>, Noritoshi Araki<sup>2</sup>, Motoki Eto<sup>2</sup>, Teruo Haibara<sup>2</sup>, Takashi Yamada<sup>2</sup>, Jochen Feldmann<sup>3</sup>, Ralph Binner<sup>3</sup>, Henk

Peters<sup>3</sup>, Achim Scheer<sup>3</sup>, Vincent Chee<sup>3</sup>

<sup>1</sup>Fraunhofer IMWS, Germany; <sup>2</sup>Nippon Micrometal Corporation,

Japan; 3ELMOS Semiconductor SE, Germany

COPPER PUMPING ANALYSIS FOR CU/SIO2 HYBRID BONDING 11:55 am -

12:15 pm **USING IN-SITU SPM IMAGING**

Ali Roshanghias<sup>1</sup>, Jaroslaw Kaczynski<sup>1</sup>, Ude Hangen<sup>2</sup>

<sup>1</sup>Silicon Austria Labs GmbH, Austria; <sup>2</sup>Bruker Nano GmbH, Germany

UNDERSTANDING THE CONTACT RESISTANCE IN AN ACF 12:15 pm -

12:35 pm **BONDING**

Helge Kristiansen<sup>1</sup>, Knut Eilif Aasmundtveit<sup>2</sup>, Giang Nghiem<sup>2</sup>,

Molly Bazilchuk<sup>3</sup>

<sup>1</sup>Conpart AS, Norway; <sup>2</sup>University of South-Eastern Norway, Norway;

<sup>3</sup>Ducky AS, Norway

**Lunch - Exhibition** 12:35 pm -

1:40 pm

2B: MFMS/SFNSORS

Session Chair: Andrew Holland, RF Module And Optical Design Ltd., UK

→ Location: Rosalind Franklin Pavilion

MEMS MIRROR IN HERMETIC PACKAGE FOR ENHANCED 11:15 am -

**PERFORMANCES** 11:35 am

> <u>Luca Maggi</u><sup>1</sup>, Marco Del Sarto<sup>1</sup>, Amedeo Maierna<sup>1</sup>, Mark Shaw<sup>1</sup>, Roberto Carminati<sup>1</sup>, Gianluca Mendicino<sup>1</sup>, Davide Rotta<sup>2</sup>, Marco

Chiesa<sup>2</sup>, Aina Serrano<sup>2</sup>, Antonella Bogoni<sup>3</sup>

<sup>1</sup>STMicroelectronics, Italy; <sup>2</sup>CamGraPhIC, Italy; <sup>3</sup>Sant'Anna School of

Adanced Studies, Italy

11:35 am -INNOVATIVE SILICON-CERAMIC (SICER) TECHNOLOGY FOR

HIGH-STRENGTH PRESSURE SENSOR APPLICATION USING 11:55 am

**DIFFERENT MANUFACTURING METHODS**

Cathleen Kleinholz<sup>1</sup>, Michael Fischer<sup>1</sup>, Nam Gutzeit<sup>1</sup>, Andrea Cyriax<sup>2</sup>,

Michael Hintz<sup>2</sup>, Thomas Ortlepp<sup>2</sup>, Jens Müller<sup>1</sup>

<sup>1</sup>Technische Universität Ilmenau, Germany; <sup>2</sup>CiS Forschungsinstitut

für Mikrosensorik GmbH, Germany

FROM MEMS STRIP TO MEMS UNIT: A COMPREHENSIVE 11:55 am -

SIMULATION APPROACH TO WARPAGE 12:15 pm

> Andrea Ratti<sup>1</sup>, Daniele Simoncini<sup>1</sup>, Annbel Adolfo<sup>2</sup>, Marco Del Sarto<sup>1</sup>, Patrick Fedeli<sup>1</sup>, Alex Gritti<sup>1</sup>, Luca Maggi<sup>1</sup>, Teresa Napolitano<sup>1</sup>, Mark

Andrew Shaw<sup>1</sup>, Jefferson Talledo<sup>2</sup>

<sup>1</sup>STMicroelectronics, Italy; <sup>2</sup>STMicroelectronics, Philippines

12:15 pm -GAS PERMEABLE PROTECTION CAPS FOR WAFER LEVEL CHIP SCALE PACKAGING (WLCSP) OF MEMS ENVIRONMENTAL SEN-

**SORS**

Ole Behrmann, Thomas Lisec, Björn Gojdka

Fraunhofer ISIT, Germany

**Lunch - Exhibition** 12:35 pm -

1:40 pm

12:35 pm

20 21

# 3A: SUBSTRATES – THICK FILM AND CU INTERCONNECTS

#### Session Chair: Jens Müller, TU Ilmenau, Germany

→ Location: Main Conference Room

2:15 pm – ADDITIVE METALLIZATION OF ALUMINA WITH COPPER-TITANI-2:35 pm UM POWDER BLENDS FOR POWER ELECTRONIC APPLICATIONS

<u>Christoph Hecht</u><sup>1</sup>, Eric Schadow<sup>1</sup>, Mario Sprenger<sup>1</sup>, Felix Häußler<sup>1</sup>,

Thomas Stoll<sup>2</sup>, Jörg Franke<sup>1</sup>

<sup>1</sup>|Friedrich-Alexander-Universtität Erlangen-Nürnberg, Nuremberg, Germany; <sup>2</sup>TUM School of Engineering and Design, Munich, Germa-

ny

2:35 pm – NEGATIVE-TONE PHOTO-DEFINABLE POLYIMIDE WITH HIGH

2:55 pm THERMAL STABILITY AND THICK FILM PROCESSABILITY

<u>Hitoshi Araki</u>, Takayuki Kaneki, Yu Shoji, Chika Hibino

Toray Industries Inc., Japan

2:55 pm - DIP BASED ALL CU INTERCONNECTS

3:15 pm Richard Dixon<sup>1</sup>, Luca Del Carro<sup>2</sup>, Thomas Brunschwiler<sup>2</sup>

<sup>1</sup>Dycotec Materials Ltd, United Kingdom; <sup>2</sup>IBM Research, Zurich,

Switzerland

3:15 pm - Break - Exhibition

3:45 pm

# 3B: ADHESIVES AND ENCAPSULANTS

Session Chairs: Eamonn Redmond, Inseto (UK) Ltd. UK

→ Location: Rosalind Franklin Pavilion

2:15 pm – EPOXY MOLDING COMPOUND BLEEDING REDUCTION ON

2:35 pm SURFACE MOUNT SEMICONDUCTOR DEVICE

<u>Federico Leone</u><sup>1</sup>, Fulvio Viviani<sup>1</sup>, Hidetoshi Seki<sup>2</sup>, Masami Ishii<sup>2</sup> <sup>1</sup>STMicroelectronics, Italy; <sup>2</sup>Sumitomo Bakelite Singapore Pte. Ltd,

Singapore

2:35 pm - INFLUENCE OF THERMALLY AGED UNDERFILL ON FLIP-CHIP

2:55 pm PACKAGES

Kevin Cox, Ghassan Abu-Hamdeh, Matt Borden

Tektronix Component Solutions, United States of America

2:55 pm – ADHESIVE SOLUTIONS FOR CLOSED CAVITY PACKAGING

3:15 pm Patrick Schirmer, Severin Ringelstetter

DELO Industrie Klebstoffe GmbH & Co. KGaA, Germany

3:15 pm – Break - Exhibition

3:45 pm

22 | | 23

# 4A: INTERCONNECT MATERIALS II

#### Session Chair: Krammer Olivér, BME, Hungary

→ Location: Main Conference Room

3:45 pm – DEVELOPMENT OF A STRETCHABLE AND REMOVABLE

4:05 pm ELECTRICAL INTERCONNECTION SOLUTION FOR ULTRA-THIN

**ELECTRONIC COMPONENTS**

<u>Auriane Despax-Ferreres</u><sup>1</sup>, Pascal Tiquet<sup>1</sup>, Jean-Charles Souriau<sup>2</sup>,

Vincent Jousseaume<sup>2</sup>, Julia De Girolamo<sup>1</sup>

<sup>1</sup>Univ. Grenoble Alpes, CEA, Liten, Grenoble, France; <sup>2</sup>Univ. Grenoble Alpes, CEA, Leti, Grenoble, France

4:05 pm – UV LASER COPPER PAD SURFACE EXPOSURE FOR LASER DIRECT

4:25 pm STRUCTURING (LDS) OF INTERCONNECTION

Guendalina Catalano, <u>Alessandro Mellina Gottardo</u>, Riccardo Villa

ST microelectronics, Italy

4:25 pm – THE FORMATION OF AG NODULES ON FINE AG-SI PARTICLES

4:45 pm Koji Nakayama¹, Minoru Ueshima², Masahiko Nishijima¹, Takeshi

Sakamoto<sup>2</sup>, Chuantong Chen<sup>1</sup>, Katsuaki Suganuma<sup>1</sup> <sup>1</sup>Osaka University, Japan; <sup>2</sup>Daicel Corporation, Japan

4:45 pm - FINE PITCH MICRO INDIUM BUMP INTERCONNECT FLIP CHIP

5:05 pm BONDING

Travis Scott

Finetech GmbH & Co.KG, Germany

Exhibition, Poster, Pizza

7:00 pm

5:10 pm -

# 4B: MEDICAL

Session Chair: Anne Vanhoestenberghe, King's College London, UK

→ Location: Rosalind Franklin Pavilion

3:45 pm – INITIAL LIFE TEST OF SILICONE ENCAPSULATED FR4 PRINTED

4:05 pm CIRCUIT BOARDS FOR PRE-CLINICAL ACTIVE IMPLANTS

CINCOTT BOARDSTORTRE CEIMORERCHVE IMI EMITS

Ishpa Ali¹, Fei Xue¹, Carlos Perez Henriquez¹, Thomas Niederhoffer¹,

Ahmad Shah Idil<sup>1</sup>, Dai Jiang<sup>2</sup>, <u>Henry Thomas Lancashire</u><sup>1</sup>

<sup>1</sup>Department of Medical Physics and Biomedical Engineering,

University College London, London, UK.; <sup>2</sup>Department of Electronic and Electrical Engineering, University College London, London, UK.

4:05 pm - VOIDING IN PARYLENE-C ENCAPSULATION OF SURFACE MOUNT

4:25 pm LEDS FOR AN OPTOGENETIC EPILEPSY NEUROPROSTHESIS

Ahmad Shah Idil<sup>1</sup>, Richard Bailey<sup>2</sup>, Johannes Gausden<sup>2</sup>, Antony

O'Neill<sup>2</sup>, Nick Donaldson<sup>1</sup>

<sup>1</sup>University College London, UK; <sup>2</sup>Newcastle University, UK

4:25 pm – ASSEMBLY OF PRINTED INTERCONNECTS FOR IMMOBILIZED

4:45 pm PROTEIN MICROFLUIDIC ASSAYS

Qianwen Xu<sup>1</sup>, Jeffery C. C. Lo<sup>1</sup>, Yusong Guo<sup>1</sup>, S. W. Ricky Lee<sup>1,2,3</sup>

<sup>1</sup>The Hong Kong University of Science and Technology, Hong Kong, PRC; <sup>2</sup>HKUST Shenzhen-Hong Kong Collaborative Innovation Research Institute, PRC; <sup>3</sup>HKUST LED-FPD Technology R&D Center

at Foshan, PRC

4:45 pm - FLEXIBLE HYBRID ELECTRONICS ON WEARABLE HEALTHCARE

5:05 pm APPLICATION

Ming-Hung Chen

ASE, Taiwan

5:10 pm – Exhibition, Poster, Pizza

7:00 pm

24 | | 25

## POSTER SESSION

# O1 TESTING OF ELECTROMIGRATION RESISTANCE OF COPPER AND SILVER THICK FILMS

<u>Jiri Hlina</u><sup>1</sup>, Jan Reboun<sup>1</sup>, Marek Simonovsky<sup>2</sup>, Ales Hamacek<sup>1</sup>

<sup>1</sup>University of West Bohemia, Faculty of Electrical Engineering, Czech Republic; <sup>2</sup>Elceram a.s., Hradec Kralove, Czech Republic

# O2 RELIABILITY TESTING OF RECYCLED SMD COMPONENTS REUSED IN E-TEXTILES AFTER AGEING BY WASHING CYCLES

Martin Hirman, Jiří Navrátil, Andrea Benešová, František Steiner University of West Bohemia, Czech Republic

# PROCESS WINDOW OF MINI-LED DISPLAY PANEL PACKAGING USING LASER ASSISTED BONDING TECHNOLOGY

Yong Sung Eom, Gwang-Mun Choi, Ki-Seok Jang, Ji-Ho Joo, Chan-Mi Lee, Jin-Heuk Oh, Seok-Hwan Moon, Kwang-Seong Choi ETRI, Republic of South Korea

# O4 EFFECT OF SURFACE MICROSTRUCTURE ON JOINTS USING NANOPOROUS CU SHEET FOR POWER DEVICES

Hiroshi Nishikawa<sup>1</sup>, Byungho Park<sup>2</sup>, Mikiko Saito<sup>3</sup>, Jun Mizuno<sup>3</sup>

<sup>1</sup>Joining and Welding Research Institute, Osaka Universit, Japan; <sup>2</sup>Graduate School of Engineering, Osaka University, Japan; <sup>3</sup>Research Organization for Nano & Life Innovation, Waseda University, Japan

# O5 INVESTIGATION OF ALUMINUM AND GOLD FLIP-CHIP BONDING FOR QUANTUM DEVICE INTEGRATION

Imants Cirulis<sup>1</sup>, Uwe Zschenderlein<sup>2</sup>, Silvia Braun<sup>1</sup>, Moritz Radestock<sup>1</sup>, Remi Pantou<sup>1</sup>, Klaus Vogel<sup>1</sup>, <u>Franz Selbmann</u><sup>1</sup>, Steffen Kurth<sup>1</sup>, Bernhard Wunderle<sup>1,2</sup>, Harald Kuhn<sup>1,2</sup>

<sup>1</sup>Fraunhofer Institute for Electronic Nano Systems, Germany; <sup>2</sup>Technical University Chemnitz, Germany

#### POSTER SESSION • TUESDAY, SEPT. 12 • 5:10 PM - 7:00 PM

# O6 ADHESION COPPER/MOLDING COMPOUND: MODELING AND CHARACTERIZATION

Marco Rovitto<sup>1</sup>, <u>Samuele Zalaffi</u><sup>1</sup>, Carlo Passagrilli<sup>1</sup>, Claudio Maria Villa<sup>1</sup>, Luca Andena<sup>2</sup>, Stefano Mariani<sup>2</sup> <sup>1</sup>STMicroelectronics, Italy; <sup>2</sup>Polytechnic University of Milan, Italy

# O7 A HIGH-DENSITY ORGANIC PACKAGE SOLUTION TO W-BAND SIGE FLIP-CHIP APPLICATIONS

<u>Fırat Altuntaş</u>, Nihan Öznazlı, Olcay Kalkan, Emrah Koç Aselsan A.Ş, Turkey

# 08 THERMAL DESIGN OF STACKED POWER MODULES FOR ELECTRIC DRIVE APPLICATIONS

<u>Jianfeng Li</u>, Yuekang Du, Xingzhi Wang, Liangjie Liu, Yong Pang, Feixiang Liu Zhuzhou CRRC Times Electric UK Innovation Centre, United Kingdom

# O9 LAMINATION OF CAPACITIVE MICROMACHINED ULTRASONIC TRANSDUCER ON A PIEZOELECTRIC ARRAY: PROCESS AND EVALUATION Duy Hoang Le, Tung Manh, Lars Hoff

University of South-Eastern Norway (USN), Norway

# 10 ASSEMBLY OF ULTRA-THIN MEMS DEVICE ON DRIVER CHIP USING ANISOTROPIC CONDUCTIVE FILM

<u>Hoang-Vu Nguyen</u>, Knut Eilif Aasmundtveit University of South-Eastern Norway, Norway

# AN INNOVATIVE CONFORMAL ELECTRONICALLY SCANNED ARRAY ANTENNA FOR FULL 360° STEERABILITY IN THE KA-BAND

<u>Peter Uhlig</u>, Aline Friedrich, Markus Krengel, Winfried Simon, Oliver Litschke IMST GmbH, Germany

# 12 THERMALLY CONDUCTIVE POLYMER COMPOSITES WITH HEXAGONAL BORON NITRIDE FOR MEDICAL DEVICE THERMAL MANAGEMENT

Nu Bich Duyen Do<sup>1</sup>, Kristin Imenes<sup>1</sup>, Knut E. Aasmundveit<sup>1</sup>, Hoang-Vu Nguyen<sup>1</sup>, Erik Andreassen<sup>1,2</sup>

<sup>1</sup>University of South-Eastern Norway, Norway; <sup>2</sup>SINTEF Industry, Norway

#### MICROSTRUCTURAL BASED RELIABILITY INVESTIGATION OF WATER-AND SUSPENSION FREE PREPARED INTEGRATED ELECTRONIC PACKAGES Sandy Klengel, Robert Klengel, Tino Stephan Fraunhofer IMWS, Germany

# 14 NUMERICAL STUDY ON THE INFLUENCE OF POLYIMIDE THICKNESS AND CURING TEMPERATURE ON WAFER BOW IN WAFER LEVEL PACKAGING

<u>Prashant Kumar Singh</u><sup>1,2</sup>, Patrick Rohlfs<sup>1</sup>, Gunther Sandmann<sup>1</sup>, Kashi Vishwanath Machani<sup>1</sup>, Dirk Breuer<sup>1</sup>, Karsten Meier<sup>2</sup>, Frank Kuechenmeister<sup>1</sup>, Marcel Wieland<sup>1</sup>, Karlheinz Bock<sup>2</sup>

<sup>1</sup>GlobalFoundries Dresden Module One LLC & Co. KG, Germany; <sup>2</sup>Technische Universität Dresden, Institute of Electronic Packaging Technology, Germany

# 15 IMPROVEMENT OF BONDING STRENGTH AND THERMAL SHOCK RELIABILITY FOR AG SINTER JOINING DIRECT ON AL SUBSTRATE

<u>Chuantong Chen</u><sup>1</sup>, Ran Liu<sup>1</sup>, Koji Kobayashi<sup>2</sup>, Hideyo Osanai<sup>2</sup>, Zheng Zhang<sup>1</sup>, Katsuaki Suganuma<sup>1</sup>

<sup>1</sup>Osaka University; <sup>2</sup>DOWA POWER DEVICE Co., Ltd

# 16 INTERCONNECT STRESS TESTING AS A TOOL FOR ASSESSMENT OF RELIABILITY OF MODERN PCB'S

Marek Koscielski, Krzysztof Glinski, Dariusz Ostaszewski, Tomasz Klej, Jan Oklej, Aneta Cholaj, Wojciech Steplewski, Stefan Galinski Łukasiewicz Research Network - Tele and Radio Research Institute, Poland

# 17 HIGH SPEED TRANSMISSION CHARACTERISTICS ON GLASS BASED INTERPOSERS

<u>Satoru Kuramochi</u>, Masaya Tanaka, Takahiro Tai Dai Nippon Printing, Japan

# DESIGN, FABRICATION, AND CHARACTERIZATION OF A 4H-SIC CMOS READOUT CIRCUIT FOR MONOLITHIC INTEGRATION WITH SIC SENSORS

Romina Sattari, Henk van Zeijl van Zeijl, Guoqi Zhang Department of Microelectronics, Delft University of Technology, The Netherlands

28 | | | | | | | |

# DAY 2

# WEDNESDAY, SEPTEMBER 13, 2023

| 8:30 am –<br>9:00 am   | Networking                                                                                                                                                                    |                                               |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 9:00 am –<br>9:10 am   | Welcome: Day 2 <a href="#">Chair</a> : Anne Vanhoestenberghe, King's College London                                                                                           |                                               |

| 9:10 am –<br>9:40 am   | KEYNOTE 3: THE CHALLENGES OF INTEGRATING GRAPHENE INTO EXISTING PACKAGES  Dr. Ali Murad, Test & Packaging Engineer. Paragraf, UK                                              |                                               |

| 9:45 am –<br>10:45 am  | S 5A: SINTERING I                                                                                                                                                             | S 5B: EQUIPMENT / INSPECTION                  |

| 11:15 am –<br>12:35 pm | 6A: PHOTONICS AND OPTICS                                                                                                                                                      | S 6B: SOLDER / SOLDERING                      |

| 1:40 pm –<br>2:10 pm   | KEYNOTE 4: ADVANCED PACKAGING - CHALLENGES THAT ARE DRIVING NEW PACKAGE INNOVATION & ECOSYSTEM NEEDS Mark Gerber, Sr. Director Engineering and Technical Marketing, ASE Group |                                               |

| 2:15 pm -<br>3:15 pm   | S 7A: SINTERING II                                                                                                                                                            | S 7B: HERMETIC / CONFORMAL<br>COATINGS / TIMs |

| 3:45 pm -<br>5:05 pm   | S 8A: FLIP CHIP                                                                                                                                                               | S 8B: RELIABILITY AND<br>SUSTAINABILITY       |

| 6:00 pm –<br>10:00 pm  | Pre-dinner drinks followed by Dinner at Homerton College                                                                                                                      |                                               |

# 5A: SINTERING I

#### Session Chair: Martin Wickham, National Physical Laboratory, UK

→ Location: Main Conference Room

9:45 am - RELIABILITY OF COPPER SINTERED INTERCONNECTS UNDER

10:05 am EXTREME THERMAL SHOCK CONDITIONS

<u>Sri Krishna Bhogaraju</u><sup>1</sup>, Francesco Ugolini<sup>2</sup>, Alessio Greci<sup>2</sup>,

Gordon Elger<sup>1</sup>

<sup>1</sup>Technische Hochschule Ingolstadt, Germany; <sup>2</sup>AMX Automatrix srl,

Italy

10:05 am - RAPID SINTERING OF INKJET PRINTED CU COMPLEX INKS USING

10:25 am LASER UNDER AIR

Nihesh Mohan<sup>1</sup>, Sri Krishna Bhogaraju<sup>1</sup>, Juan Ignacio Ahuir-Torres<sup>2</sup>,

Hiren Kotadia<sup>2</sup>,<sup>3</sup>, Gordon Elger<sup>1</sup>

<sup>1</sup>Institute of Innovative Mobility, Technische Hochschule Ingolstadt, Germany; <sup>2</sup>School of Engineering, Liverpool John Moores Universi-

ty, UK; 3WMG, University of Warwick, UK

10:25 am - IMPROVING SEMICONDUCTOR RELIABILITY OF SILVER SINTER

10:45 am DIE ATTACH MATERIALS FOR LARGE DIE ON LEAD FRAME

**APPLICATIONS**

Ruud De Wit<sup>1</sup>, Edsger Smits<sup>2</sup>

<sup>1</sup>Henkel Nederland BV, The Netherlands; <sup>2</sup>Chip Integration

Technology Center (CITC), The Netherlands

10:45 am – Break - Exhibition

11:15 am

# 5B: EQUIPMENT / INSPECTION

Session Chair: Jeff Kettle, University of Glasgow, UK

→ Location: Rosalind Franklin Pavilion

9:45 am - PICK AND PLACE OF SENSITIVE CHIPS WITH VACUUM-FREE

10:05 am GECOMER® TOOLS

<u>Lukas Lorenz<sup>1</sup></u>, Thomas Ludewig<sup>1</sup>, Kai Swiecinski<sup>1</sup>, Henrik Ollmann<sup>2</sup>,

Amirabbas Razkordanisharahi<sup>2</sup>, Volker Bock<sup>1</sup>

<sup>1</sup>Fraunhofer IPMS, Germany; <sup>2</sup>INNOCISE GmbH, Germany

10:05 am - RESEARCH OF CHIP PLACEMENT ACCURACY FOR FAN-OUT WLP

10:25 am USING A NOVEL SELF-ASSEMBLY STAGE

Tadatomo Yamada, Ken Takano, Toshiaki Menjo, Shinya Takyu

LINTEC Corporation, Japan

10:25 am – ONE-PROBE NANOPROBING OF POWER DEVICES AND

10:45 am ELECTRONIC PACKAGES

Chengliang Huang<sup>1</sup>, Vignesh Viswanathan<sup>1</sup>, Greg M. Johnson<sup>2</sup>,

Andreas Rummel<sup>3</sup>, Heiko Stegmann<sup>4</sup>, Elliott Andrew<sup>5</sup>

<sup>1</sup>Carl Zeiss Pte Ltd, Singapore; <sup>2</sup>Zeiss Microscopy, United States of America; <sup>3</sup>Kleindiek Nanotechnik, Germany; <sup>4</sup>Zeiss Microscopy,

Germany; 5Zeiss Microscopy, UK

10:45 am - Break - Exhibition

11:15 am

## 6A: PHOTONICS AND OPTICS

Session Chair: Jayakrishnan Chandrappan, CSA Catapult; UK

→ Location: Rosalind Franklin Pavilion

11:15 am – STUDY OF SPATIAL DISTORTION IN INP NANOPHOTONIC

11:35 am MEMBRANES ON DIFFERENT CARRIER SUBSTRATES

Salim Abdi<sup>1</sup>, Aleksandr Zozulia<sup>1</sup>, Jeroen Bolk<sup>2</sup>, Erik Jan Geluk<sup>2</sup>,

Yuqing Jiao<sup>1</sup>, Kevin Williams<sup>1</sup>

<sup>1</sup>Eindhoven Hendrik Casimir Institute (EHCI), Eindhoven University of Technology; <sup>2</sup>Nanolab@tu/e, Eindhoven University of Technology

11:35 am – LASER-ASSISTED BONDING APPROACH FOR PHOTONIC

11:55 am INTEGRATION PROCESSES

<u>Aleksandr Vlasov</u>, Topi Uusitalo, Evgenii Lepukhov, Heikki Virtanen,

Samu-Pekka Ojanen, Jukka Viheriälä, Mircea Guina

Tampere University, Finland

11:55 am – INTEGRATION OF MULTI-LITHOGRAPHY TECHNOLOGIES FOR

12:15 pm THE FABRICATION OF FLEXIBLE OPTICAL LINK

Akash Sunilkumar Mistry, Krzysztof Kamil Nieweglowski,

Karlheinz Bock

Technical University of Dresden, Germany

12:15 pm - HYBRID LITHOGRAPHY FABRICATION OF SINGLE MODE OPTICS

12:35 pm FOR SIGNAL REDISTRIBUTION AND COUPLING

<u>David Weyers</u>, Krzysztof Nieweglowski, Karlheinz Bock

Technological University Dresden, Germany

12:35 pm – Lunch - Exhibition

1:40 pm

34 l

## 6B: SOLDER / SOLDERING

Session Chair: Attila Géczy, BME University, Hungary

→ Location: Main Conference Room

11:15 am - COMPARING THE SOLDERABILITY OF DIFFERENT SAC0307

11:35 am COMPOSITE SOLDER PASTES

Balázs Illés<sup>1,2,</sup> Halim Choi<sup>1</sup>, Agata Skwarek<sup>2</sup>

<sup>1</sup>Budapest University of Technology and Economics, Hungary; <sup>2</sup>Łukasiewicz Research Network - IMiF, LTCC Technology and

Printed Electronics Research Group, Poland

11:35 am – ANISOTROPIC SOLDER PASTE (ASP) MATERIAL SOLUTION FOR

11:55 am LASER ASSISTED BONDING (LAB) PROCESS

<u>Ki-Seok Jang</u>, Yong-Sung Eom, Gwang-Mun Choi, Ji-Ho Joo, Jin-Hyuk Oh, Chan-Mi Lee, Yoon-Hwan Moon, Seok-Hwan Moon,

Kwang-Seong Choi

Electronics and Telecommunication Research Institute, Republic of

South Korea

11:55 am – DURABILITY OF LEAD-FREE SOLDER INTERCONNECTIONS FOR

12:15 pm PRINTED CIRCUIT BOARD APPLICATIONS: COMPARING ENER-

GY-BASED THERMO-MECHANICAL FATIGUE MODELS

Chien-Ming Huang, Jeffrey W. Herrmann

University of Maryland, United States of America

12:35 pm – Lunch - Exhibition

1:40 pm

135

# 7A: SINTERING II

#### Session Chair: Andy Longford, PandA Europe; UK

→ Location: Main Conference Room

2:15 pm – AN EXPERIMENTAL INVESTIGATION OF A FLEXIBLE SINTERED

2:35 pm SILVER JOINT FOR MICRO-JOINING BASED ON A DESIGN OF EXPERIMENTS

<u>Laurent Vivet</u><sup>1</sup>, Lahouari Benabou<sup>2</sup>, Olivier Simon<sup>2</sup>

<sup>1</sup>VALEO, THS Material Laboratory, France; <sup>2</sup>UVSQ, University of

Paris-Saclay, France

2:35 pm – UNDERSTANDING CU SINTERING AND ITS ROLE ON CORROSION

2:55 pm BEHAVIOUR FOR HIGH-TEMPERATURE MICROELECTRONIC APPLICATION

Juan Ignacio Ahuir-Torres<sup>1</sup>, Sri Krishna Bhogaraju<sup>2</sup>, Geoff West<sup>3</sup>,

Gordon Elger<sup>2</sup>, Hiren Kotadia<sup>1,3</sup>

<sup>1</sup>Liverpool John Moores University, UK; <sup>2</sup>Technische Hochschule

Ingolstadt, Germany; 3The University of Warwick, UK

2:55 pm – INSPECTION TECHNIQUES USING SCANNING ACOUSTIC

3:15 pm MICROSCOPY FOR SILVER SINTERING APPLICATIONS IN POWER ELECTRONIC MODULES

Heaklig Ayala<sup>1,2</sup>, Jose Ortiz-Gonzalez<sup>1</sup>, Mohamed-Amer Karout<sup>1</sup>,

James Cotty<sup>2</sup>, Tim Rumney<sup>2</sup>, Philip Mawby<sup>1</sup>

<sup>1</sup>University of Warwick, United Kingdom; <sup>2</sup>Custom Interconnect

Limited, United Kingdom

3:15 pm – E

**Break - Exhibition**

# 7B: HERMETIC/CONFORMAL COATINGS/TIMS

Session Chair: Hassan Akhtar, Manufacturing Technology Centre

→ Location: Rosalind Franklin Pavilion

2:15 pm – CHARACTERIZATION OF A NOVEL COST-EFFICIENT AND

2:35 pm ENVIRONMENTALLY FRIENDLY GRAPHENE-ENHANCED THERMAL

INTERFACE MATERIAL

<u>Sihua Guo</u><sup>1</sup>, Kristoffer Harr (Martinsen)<sup>2</sup>, Amos Nkansah<sup>2</sup>, Jiajia Chen<sup>1</sup>, Zhiyang Shen<sup>1</sup>, Murali Murugesan<sup>2</sup>, Hongfeng Zhang<sup>2</sup>, Lars

Almhem<sup>2</sup>, Arto Ahtonen<sup>2</sup>, Jin Chen<sup>3</sup>, Johan Liu<sup>1,4,5</sup>

<sup>1</sup>SMIT Center, Shanghai University, PRC; <sup>2</sup>SHT Smart High-Tech AB, Sweden; <sup>3</sup>Shanghai Ruixi New Materials High Tech Co. Ltd., PRC; <sup>4</sup>Electronics Materials and Systems Laboratory, Chalmers University of Technology, Sweden; <sup>5</sup>School of Energy and Materials Science,

Shanghai Poly-Tech University, PRC

2:35 pm – EVOLUTION OF GETTER TECHNOLOGY IN ELECTRONIC

2:55 pm HERMETIC PACKAGING

Luca Mauri, <u>Giovanni Zafarana</u>, Enea Rizzi, Alessio Corazza

SAES Getters, Italy

2:55 pm – ADVANCES IN PARYLENE ADHESIVE BONDING FOR THE 3:15 pm REALIZATION OF BIOCOMPATIBLE MICROSYSTEMS

Franz Selbmann<sup>1,2</sup>, Frank Roscher<sup>1</sup>, Maik Wiemer<sup>1</sup>, Harald Kuhn<sup>1,3</sup>,

Yvonne Joseph<sup>2</sup>

<sup>1</sup>Fraunhofer Institute for Electronic Nano Systems ENAS, Germany; <sup>2</sup>TU Bergakademie Freiberg, Institute for Electronic and Sensor Materials, Germany; <sup>3</sup>TU Chemnitz, Center for Microtechnologies,

Germany

3:15 pm - Break - Exhibition

3:45 pm

## 8A: FLIP CHIP

#### Session Chair: John Lipp, STFC, UK

→ Location: Main Conference Room

3:45 pm – FLIP-CHIP INTERCONNECTS BASED ON SINGLE METAL-COATED 4:05 pm POLYMER SPHERES

<u>Van Long Huynh</u>, Knut Eilif Aasmundtveit, Hoang-Vu Nguyen

University of South-Eastern Norway, Norway

4:05 pm – 20μM COPPER MICRO-BUMP BONDING THROUGH A SILVER 4:25 pm METALLIZATION FOR ADVANCED PACKAGING UNDER A

LOW-PRESSURE CONDITION

Zheng Zhang<sup>1</sup>, M.-C. Hsieh<sup>1</sup>, A. Suetake<sup>1</sup>, H. Yoshida<sup>1</sup>, R. Okumuara<sup>1</sup>, N. Kagami<sup>1</sup>, Kazamasa Okamoto<sup>1</sup>, Chuantong Chen<sup>1</sup>, Kei Hashizume<sup>2</sup>, N. Hasegawa<sup>2</sup>, R. Yoshida<sup>2</sup>, H. Homma<sup>2</sup>, K. Suganuma<sup>1</sup> SANKEN, Osaka University, Japan; <sup>2</sup>Okuno Chemical Industries Co.

Ltd.

4:25 pm – PRACTICAL RESULTS TO DEMONSTRATE AN INCREASE IN THE 4:45 pm RELIABILITY OF FLIP CHIP CONNECTIONS BY ADDING NANO-

**PARTICLES TO SOLDER**

<u>David Harvey</u><sup>1</sup>, Teresa Manzanera<sup>2</sup>, Kangkana Baishya<sup>3</sup>, Guangming Zhang<sup>1</sup>, Mohd Arif Anuar<sup>4</sup>, Y. C. Chan<sup>1</sup>, Nduka Ekere<sup>1</sup>, Derek Braden<sup>5</sup> <sup>1</sup>Liverpool John Moores University, Liverpool, UK; <sup>2</sup>University of Liverpool, Liverpool, UK; <sup>3</sup>Assam Engineering College, Guwahati,

India; 4UniMAP, Perlis, Malaysia; 5Aptiv, Coventry, UK

4:45 pm – DEVELOPMENT AND CHARACTERIZATIONS OF FINE PITCH FLIP-5:05 pm CHIP INTERCONNECTION USING SILVER SINTERING

> <u>Julie Gougeon<sup>1,2</sup></u>, Céline Feautrier<sup>1</sup>, Laurent Mendizabal<sup>1</sup>, Jean-Charles Souriau1, Mona Tréquer-Delapierre<sup>2</sup>

<sup>1</sup>CEA Leti, France; <sup>2</sup>ICMCB, France

6:00 pm – Pre-dinner drinks and Dinner at Homerton College 10:00 pm

#### 8B: RELIABILITY AND SUSTAINABILITY

Session Chair: Derek Braden, Aptiv, UK

→ Location: Rosalind Franklin Pavilion

3:45 pm – ANALYSIS OF THE IMPACT OF ENVIRONMENTAL CONDITIONS ON

4:05 pm THE RELIABILITY IN 5G PCB ASSEMBLIES

Hans Walter<sup>1</sup>, Marius van Dijk<sup>1</sup>, Julia-Marie Köszegi<sup>1</sup>, Saskia Huber<sup>1</sup>,

Olaf Wittler<sup>1</sup>, Michael Kaiser<sup>1</sup>, Martin Schneider-Ramelow<sup>1,2</sup>

<sup>1</sup>Fraunhofer IZM, Germany; <sup>2</sup>Technische Universität Berlin, Germany

4:05 pm - EVALUATION OF THE ENVIRONMENTAL IMPACT WITHIN SEMI-

4:25 pm CONDUCTOR PACKAGING MATERIALS

Andrew Bainbridge, Lewis Clark, Kathleen Grant, Jeff Kettle

University of Glasgow, United Kingdom

4:25 pm - COMBINED MEASUREMENT OF TEMPERATURE AND STRAINING

4:45 pm OF A PCB DURING OPERATION USING STEREO DIC AND

THERMAL CAMERA

<u>Guven Ogus</u><sup>1</sup>, Lukas Wittevrongel<sup>1</sup>, Pascal Lava<sup>1</sup>, Alessandro

Lambrughi<sup>2</sup>, Sam Coppieters<sup>2</sup>

<sup>1</sup>MatchID, Belgium; <sup>2</sup>KU Leuven, Belgium

4:45 pm - MEASUREMENT AND SIMULATION OF MECHANICAL STRENGTH

5:05 pm OF BACK-END-OF-LINE LAYER IN ADVANCED CMOS DIES

Bart Vandevelde<sup>1</sup>, Kevin Cox<sup>2</sup>, Reza Moloudi<sup>1</sup>, Riet Labie<sup>1</sup>, Jason

Krantz<sup>2</sup>, Matt Borden<sup>2</sup>, Kris Vanstreels<sup>1</sup>, Mario Gonzalez<sup>1</sup>

imec, Belgium; <sup>2</sup>Tektronix, United States of America

......

6:00 pm - Pre-dinner drinks and Dinner at Homerton College

10:00 pm

# DAY 3 THURSDAY, SEPTEMBER 14, 2023

| 8:30 am –<br>9:00 am   | Networking                                                                                                                                           |                       |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 9:00 am –<br>9:30 am   | KEYNOTE 5: REINVENTING ELECTRONICS FOR A SUSTAINABLE WORLD  Dr. Feras Alkhalil, Principal Scientist and Director of R&D, Pragmatic Semiconductor, UK |                       |

| 9:35 am –<br>10:35 am  | S 9A: MACHINE LEARNING                                                                                                                               | S 9B: SOLAR / SENSORS |

| 11:10 am –<br>12:30 pm | S 10A: HIGH FREQUENCY                                                                                                                                | S 10B: POWER MODULES  |

| 12:30 pm –<br>1:00 pm  | Closing Session - Awards                                                                                                                             |                       |

| 1:00 pm –<br>2:00 pm   | Light Lunch & Exhibition                                                                                                                             |                       |

40

# 9A: MACHINE LEARNING

#### Session Chair: Stephen Riches, IMAPS-UK; UK

→ Location: Main Conference Room

9:35 am – APPLICATION OF MACHINE LEARNING METHODS FOR PROCESS

9:55 am OPTIMIZATION IN ELECTRONIC PACKAGING PROCESSES

<u>Corinna Niegisch</u><sup>1</sup>, Sabine Haag<sup>1</sup>, Tanja Braun<sup>2</sup>, Ole Hölck<sup>2</sup>, Martin

Schneider-Ramelow<sup>3</sup>

<sup>1</sup>Robert Bosch GmbH, Germany; <sup>2</sup>Fraunhofer IZM Berlin, Germany;

<sup>3</sup>Technical University Berlin, Germany

9:55 am – USING DEEP LEARNING RECONSTRUCTION FOR HIGH

10:15 am THROUGH-PUT AND HIGH-RESOLUTION 3D ANALYSIS OF

**PACKAGED WAFERS**

Allen Gu<sup>1</sup>, Andrew Elliott<sup>2</sup>, Andriy Andreyev<sup>1</sup>, Masako Terada<sup>1</sup>,

Yanjing Yang<sup>1</sup>

<sup>1</sup>ZEISS Research Microscopy Solutions, United States of America;

<sup>2</sup>Carl Zeiss Ltd., United Kingdom

10:15 am – PARTIAL DISCHARGE CHARACTERIZATION OF CERAMIC POWER

10:35 am ELECTRONICS CIRCUIT CARRIERS ASSISTED BY MACHINE

**LEARNING**

<u>Johannes Drechsel</u>, Lars Rebenklau, Henry Barth

Fraunhofer IKTS, Germany

10:35 am – Break - Exhibition

11:10 am

# 9B: SOLAR / SENSORS

Chairs: Knut E Aasmundtveit, University of South-Eastern Norway, Norway

→ Location: Rosalind Franklin Pavilion

9:35 am - IMPACT OF PAD LAYOUTS AND SOLDER VOLUME ON

9:55 am SELF-ALIGNMENT OF MICRO SOLAR CELLS

Elisa Kaiser<sup>1</sup>, Maike Wiesenfarth<sup>1</sup>, Victor Vareilles<sup>2</sup>, Henning

Helmers<sup>1</sup>

<sup>1</sup>Fraunhofer ISE, Germany; <sup>2</sup>Université Grenoble Alpes, CEA LITEN,

France

9:55 am - NOVEL LOW TEMPERATURE AND LOW PRESSURE SINTERING OF

10:15 am ADAS RADAR SENSOR ANTENNA STACK

Sri Krishna Bhogaraju<sup>1</sup>, Dirk Busse<sup>2</sup>, Alexander Dahlbüdding<sup>2</sup>, Philipp

Hadrava<sup>3</sup>, Hüseyin Erdogan<sup>3</sup>, Gordon Elger<sup>1</sup>

<sup>1</sup>Technische Hochschule Ingolstadt, Germany; <sup>2</sup>Budatec GmbH,

Germany; 3Conti Temic microelectronics GmbH, Germany

Power Session (10B)

10:15 am - BACCHUS - AN ADAPTABLE FORMAT POWER MODULE FOR LOW

10:35 am VOLUME DESIGNS

Piers Tremlett

Microchip, United Kingdom

10:35 am - Break - Exhibition

11:10 am

#### **10A: HIGH FREQUENCY**

Session Chair: Ivan Ndip, Fraunhofer IZM | BTU Cottbus-Senftenberg, Germany

→ Location: Main Conference Room

11:10 am – CHARACTERIZATIONS FOR EWLB (EMBEDDED WAFER

11:30 am LEVEL BALL GRID ARRAY) ANTENNA IN MOLDED PACKAGE

INTEGRATIONS IN 77GHZ AUTOMOTIVE APPLICATIONS

M.-C. Hsieh<sup>1</sup>, F. Zhang<sup>2</sup>, F. Zhu<sup>2</sup>, K. Liu<sup>2</sup>, L. Chua<sup>3</sup>, Y. Lin<sup>3</sup>, J. Damalerio<sup>3</sup>,

Hin Hwa Goh3, Kai Chong Chan3, Zihao Chen4

<sup>1</sup>JCET Group Co. Ltd., Singapore; <sup>2</sup>Andar Technologies Co., Ltd.; <sup>3</sup>JCET Group Co. Ltd., Singapore; <sup>4</sup>Harbin Institute of Technology, Shenzhen,

PRC

11:30 am – A DUAL-BAND DUAL-POLARIZED 2X2 ANTENNA ARRAY WITH 11:50 am BEAMFORMING FOR 5G AIP AND MMWAVE APPLICATIONS

Sheng-Chi Hsieh, Wen-Chun Hsiao, Hong-Sheng Hong-Sheng,

Cheng-Yu Ho, Chen-Chao Wang

ASE group /Advanced Semiconductor Engineering, Taiwan

11:50 am – ANALYSIS AND CHARACTERIZATION OF CASTELLATED HOLES AS

12:10 pm RF INTERCONNECTS FOR MODULAR MILLIMETER-WAVE DEVICES

Paul Perlwitz<sup>1,2</sup>, Christian Tschoban<sup>1</sup>, Ivan Ndip<sup>1</sup>, Harald Pötter<sup>1</sup>,

Martin Schneider-Ramelow<sup>1,2</sup>

<sup>1</sup>TU Berlin; <sup>2</sup>Fraunhofer IZM, Germany

12:10 pm – HIGH-Q KU-BAND MICROSTRIP SPIRAL RESONATOR IN FAN-OUT 12:30 pm WAFER-LEVEL PACKAGING TECHNOLOGY FOR VCO APPLICATIONS

<u>M. Chernobryvko</u><sup>1</sup>, M. P. Kaiser<sup>1</sup>, K. S. Murugesan<sup>1</sup>, D. Kuylenstierna<sup>2</sup>, J.-M. Köszegi<sup>1</sup>, R. Gernhardt<sup>1</sup>, T. Braun<sup>1</sup>, I. Ndip<sup>1</sup>, M. Schneider-Ramelow<sup>1</sup>

<sup>1</sup>Fraunhofer IZM Berlin, Germany; <sup>2</sup>Chalmers University of

Technology, Sweden

12:30 pm – Closing session - Awards

1:00 pm

1:00 pm - Light Lunch & Exhibition

2:00 pm

# Session Chair: Andy Longford, PandA Europe, UK → Location: Rosalind Franklin Pavilion

**Light Lunch & Exhibition**

10B: POWER MODULES

THERMAL-MECHANICAL ANALYSIS OF A POWER MODULE WITH 11:10 am -PARAMETRIC MODEL ORDER REDUCTION 11:30 am Sheikh Rokibul Hassan<sup>1</sup>, Pushparajah Rajaguru<sup>1</sup>, Stoyan Stoyanov<sup>1</sup>, Christopher Bailey<sup>2</sup> <sup>1</sup>University of Greenwich, United Kingdom; <sup>2</sup>School of Electrical, Computer and Energy Engineering, Arizona State University, USA THICKNESS EFFECT OF COPPER CLIPS ON POWER MODULE 11:30 am -11:50 am **PACKAGING DESIGN** H. Wan<sup>1</sup>, N. Iosifidis<sup>1</sup>, X. Zhang<sup>1</sup>, R. Rong<sup>2</sup>, M. Antoniou<sup>1</sup>, P. Mawby<sup>1</sup> <sup>1</sup>University of Warwick, United Kingdom; <sup>2</sup>MacMic Science & Technology Co., Ltd, China 11:50 am -HIGH FREQUENCY THIN FILM MAGNETICS-ON-SILICON WITH 12:10 pm IMPROVED INDUCTANCE AND RESISTANCE Martin Sittner Würth Elektronik eiSos Group, Germany 12:10 pm -ENHANCED RELIABILITY FOR POWER MODULES VIA A NEW AG/SI SINTER JOINING STRATEGY 12:30 pm Y. Liu<sup>1</sup>, C. Chen<sup>1</sup>, Koji S. Nakayama<sup>1</sup>, Minoru Ueshima<sup>2</sup>, Takeshi Sakamoto<sup>2</sup>, Takuya Naoe<sup>3</sup>, Hiroshi Nishikawa<sup>3</sup>, Katsuaki Suganuma1 <sup>1</sup>Flexible 3D System Integration Laboratory, Osaka University, Japan; <sup>2</sup>Daicel Corporation, Japan; <sup>3</sup>Joining and Welding Research Institute, Osaka University, Japan Closing session - Awards 12:30 pm -1:00 pm

45

1:00 pm -2:00 pm

#### **NETWORKING EVENTS**

# WELCOME RECEPTION

Monday 11 September 20233 at Homerton College, Cambridge // 6:00 pm - 7:30 pm

We will be kicking off this year's conference with a welcome drinks and canapes reception at Homerton College. Don't miss the chance to get the lay of the land and meet the other conference delegates before heading into the hustle and bustle of the conference program. Afterwards you are free to choose from a selection of local restaurants within walking distance.

Sponsored by

# EXHIBITION, POSTER & PIZZA

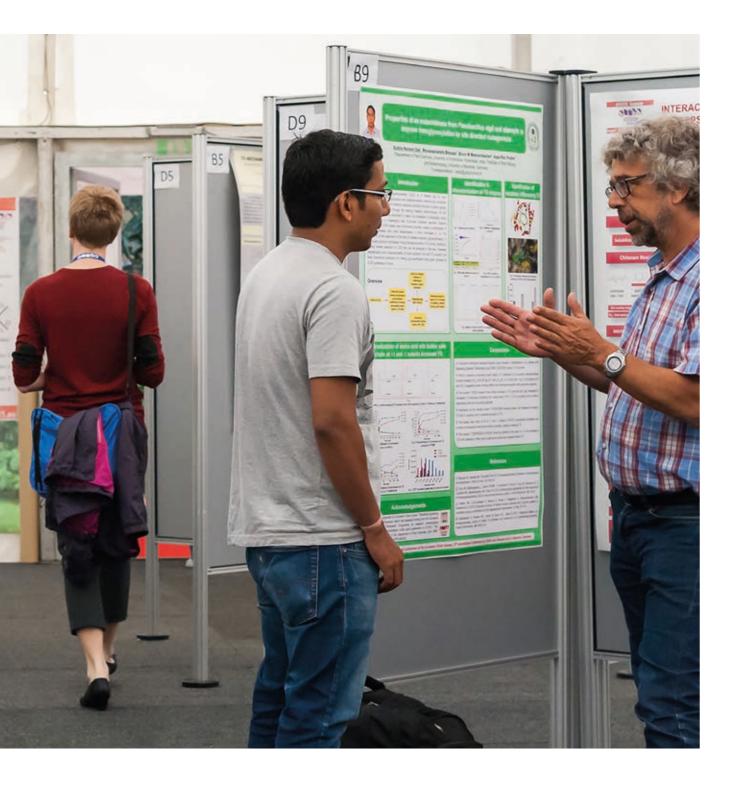

Tuesday 12 September 2023 at the Genome Center // 5:10 pm - 7:00 pm

Your chance to take a stroll around the exhibition booths and check out the posters as well. The presenters will be there to explain their research in detail and the exhibitors will be happy to answer your questions about their product and service portfolio. Oh, and there will be pizza and refreshments.

## CONFERENCE DINNER

Wednesday 13 September 2023 at Homerton College, Cambridge // 6:00pm-10:00pm

A Conference Dinner has been organised at Homerton College Cambridge on Wednesday 13 September 2023, in the spacious, modern Dining Hall (picture of Exterior), where Conference Delegates will have the opportunity to network with fellow attendees and enjoy a three course meal and refreshments as part of the Conference ticket.

Sponsored by

# **THANK YOU** TO ALL OUR SPONSORS AND EXHIBITORS

eurofins

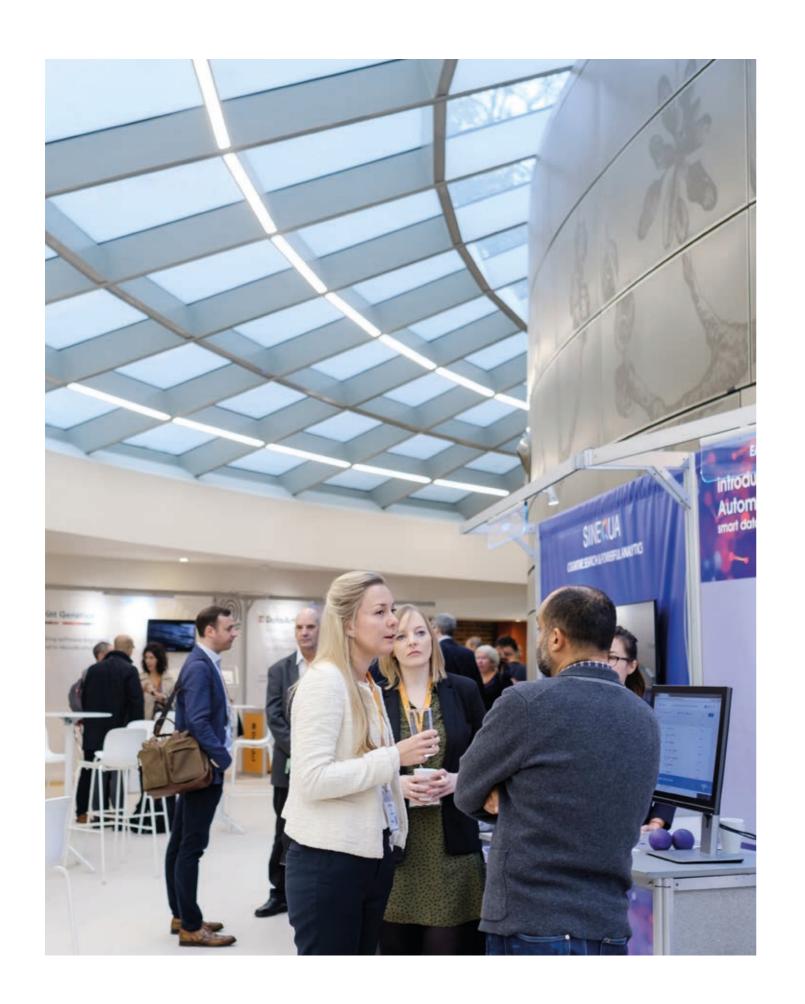

# PLATINUM, GOLD AND SILVER EXHIBITORS SHOWCASE

Besi is a leading supplier of semiconductor assembly equipment and develops cutting edge assembly processes and equipment for a variety of semiconductor applications.

# Drivers of Innovation

Besi is proud to sponsor the EMPC 2023.

www.besi.com

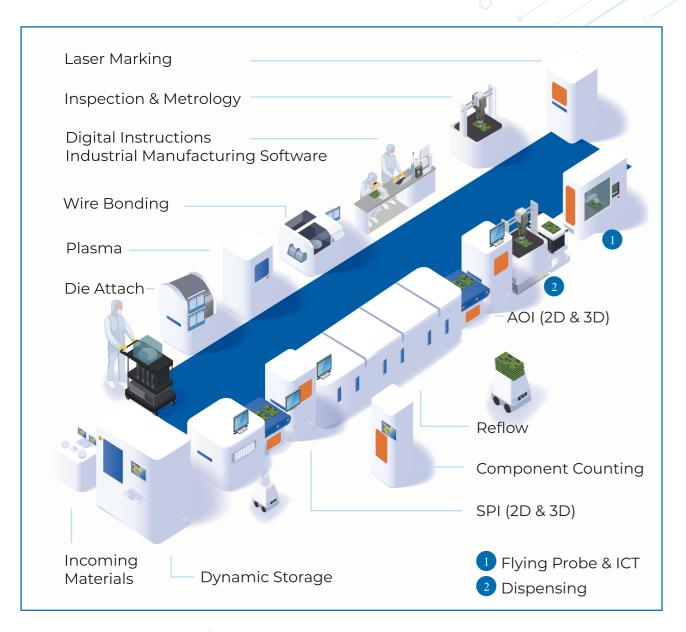

# SUPPLIER OF EQUIPMENT FOR MICROELECTRONICS & PCB ASSEMBLY

www.accelonix.co.uk

# **ADVANCED PACKAGING EQUIPMENT & WAFER LEVEL PACKAGING SERVICES**

ADVANCED

PACKAGING

EQUIPMENT

- LASER SOLDERING

- LASER ASSISTED BONDING

- ELECTROLESS PLATING

- SOLDER BALL MOUNTING

- WIRE SOLDERING

• ELECTROLESS PLATING

- ELECTROPLATING

- COPPER PILLAR

- REDISTRIBUTION LAYER

- SOLDER BALLING

- WAFER DICING/THINNING

WAFER

**LEVEL**

**PACKAGING**

**SERVICES**

pactech.com

LEADING TECHNICAL DISTRIBUTOR OF EQUIPMENT AND RELATED MATERIALS TO THE

# MICROELECTRONIC AND **ADVANCED TECHNOLOGY SECTORS**

#### **ADHESIVES**

A comprehensive range of technical adhesives and sealants for the automotive. electronic and general manufacturing industries

#### **EQUIPMENT**

Providing fabrication, assembly and test equipment for research and production of semiconductor devices and related technologies

#### **MATERIALS**

For assembly materials and machine consumable products used in microelectronic. photonic and high-frequency devices

Call: +44 (0)1264 334505 enquiries@inseto.co.uk inseto.co.uk

#### **WAFERS**

A wide range of wafers and substrates supplied worldwide, including silicon, compound semiconductor and glass materials

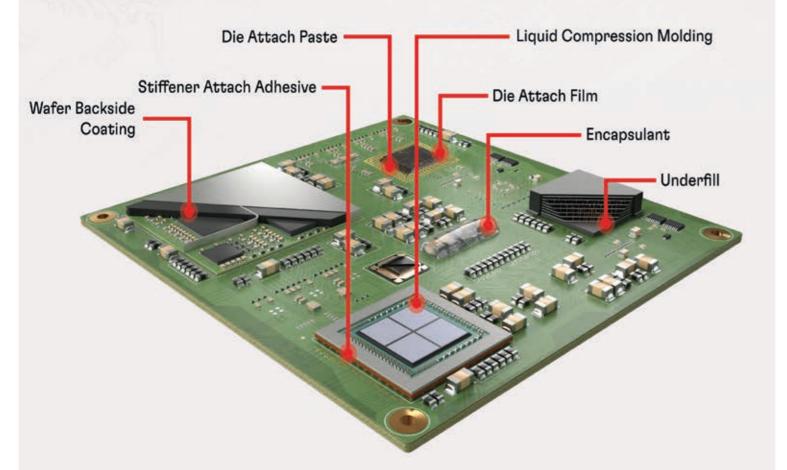

manufacturing services in assembly and test introduces... /IPack

An advanced packaging platform designed to enable vertically integrated package solutions.

The world's leading global provider of semiconductor

"Our expanding digitized world is driving unparalleled innovation across the semiconductor industry and VIPack™ represents a crucial leap forward in the transformational packaging technologies required to achieve the highly complex system integration our customers need to remain competitive," said Yin Chang, Senior Vice President of Sales and Marketing. "Through VIPack™, we're empowering our customers to discover new efficiencies in their semiconductor design and manufacturing process and

"ASE is delighted to bring its VIPack™ platform to market, opening up new opportunities for our customers to innovate from the design process all the way to production and to reap extensive benefits in relation to functionality, performance, and cost," said Dr. C.P. Hung, Vice President of R&D, ASE. "As the world's leading OSAT, ASE is strategically positioned to help customers improve efficiency, speed

time-to-market, and sustain profitable growth. VIPack™ underscores our commitment to deliver our most innovative packaging technologies to date."

> Available now, ASE's VIPack™ is a scalable platform that will expand in alignment with industry roadmaps

to reimagine the integration technologies required to accomplish application excellence."

# **ENABLING THE NEXT GENERATION** OF SEMICONDUCTOR PACKAGING

Assembly Films | Conductive and Insulating Adhesives | Optically Clear Encapsulants | Polyimide Tapes | Bonding Wires | Solder Spheres | Thermal Interface Materials Semiconductor Molding Compounds | Optoelectronic Molding Compounds | Surface Treatments | Leadframes | Semiconductor Mold Maintenance | Mold Release Sprays

**Compound Semiconductor Applications** (CSA) Catapult is the UK's authority on compound semiconductor applications and commercialisation.

CSA Catapult helps businesses solve the technical problems they face when taking their products and applications to market, using our expertise, know-how and state-of-the-art equipment.

Our diverse team of semiconductor and compound semiconductor packaging experts Industrialisation Centre (DER-IC) help businesses to develop next-generation technology across Power Electronics, RF & Microwave and Photonics through carries out multi-material, metal, innovative package design, modelling, thermal management, assembly and testing.

CSA Catapult is home to the Driving the Electric Revolution for the South West and Wales. Our state-of-the-art 3D printing capability, unique to the UK, and ceramic 3D packages, heat sinks, and embedded packaging

#### Find out how we can help you:

csa.catapult.org.uk collaboration@csa.catapult.org.uk

- CSACatapult

- n Compound Semiconductor Applications (CSA) Catapult

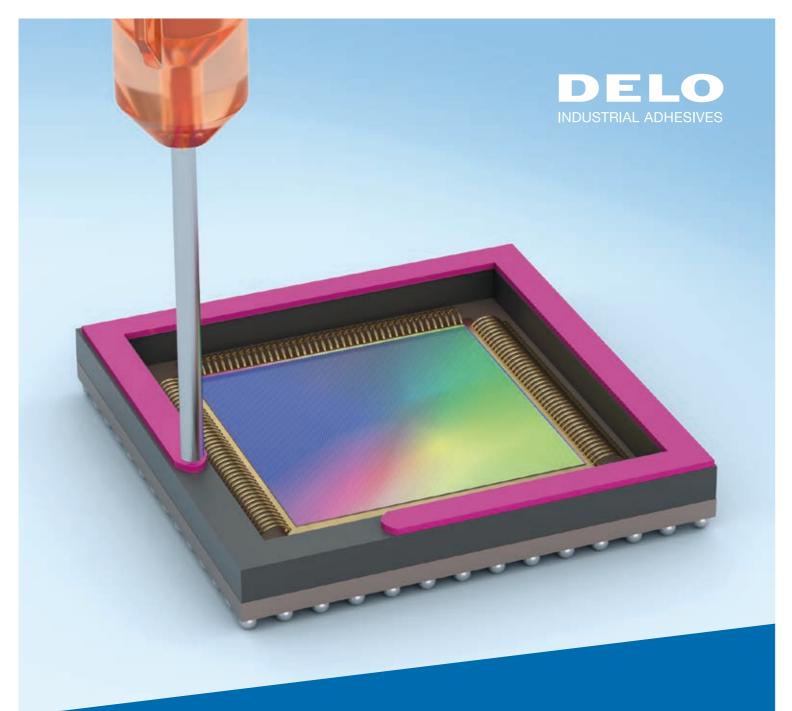

# High-tech adhesives

for semiconductors

DELO adhesives offer highest reliability tested according to AEC-Q100 for closed cavity packaging such as in automotive image sensors.

Find out more go.DELO.de/empc23 **European Microelectronics & Packaging Conference**Hall 13, September 11 – 14, 2023

#### Total Solution Provider for Dicing, Grinding and Polishing

DISCO is a total solution provider for Dicing (*Kiru*), Grinding (*Kezuru*) and Polishing (*Migaku*) technologies.

We manufacture and sell precision dicing, grinding, polishing machines and also dicing blades and grinding/polishing wheels. We are also providing ablation laser and stealth laser cutting, and plasma dicing solutions.

Our unique advantage is that we can provide you with not only machines and consumables, but also the total process solutions based on our wide range of application experiences.

Dicing-Grinding Service and Camtek optical inspection service are available in our cleanroom at Munich office. We accept orders even from a small quantity.

Please also visit <a href="https://www.dicing-grinding.com/">https://www.dicing-grinding.com/</a>

#### DISCO HI-TEC EUROPE GmbH

Liebigstrasse 8

85551 Kirchheim b. München,

Germany

Phone: +49 (0)89 909030

General inquiries:

contactsales@discoeurope.com

www.discoeurope.com

www.dicing-grinding.com

#### **FAILURE ANALYSIS & RELIABILITY TEST**

#### **FAILURE ANALYSIS**

- Non-destructive Analysis

- Failure Localization

- Package Decapsulation

- FIB Circuit Edit

- DPA/Construction Analysis

- IPC-A-600/610 PCB Inspection

- Complete RMA flow

#### **RELIABILITY TEST**

- ESD & Latch Up Testing

- AEC-Q100 Qualification

- JEDEC Qualification

- System Level Testing

- Mechanical Testing

- Environmental Testing

- HALT Robustness Testing

# Forensic problem solving for electronics

#### **MCS Investigations**

Problem solving for materials, manufacturing and reliability

#### **MCS** Assurance

Continuous quality assurance at the microscopic level

#### **MCS** Research

Materials consultancy for your product development

the MCS group.co.uk

# **Surfx Technologies**

#### **Atmospheric-Pressure Plasma Systems**

Surfx Technologies' atmospheric-pressure argon plasma systems are designed to clean and activate substrates for improved adhesion. They are ideal for semiconductor packaging and electronics manufacturing. Turnkey automated systems come standard with in-line conveyance for high-volume manufacturing. An optional drawer can be installed for high-mix, low-volume production. Integrator packages enable plasma cleaning inside bonders.

Surfx's Atomflo™ controller operates with low voltage, radio frequency (RF) power, and generates a uniform, particle free, and electrically neutral plasma that is safe on the most sensitive electronics.

Surfx plasma systems offer many options for in-line or batch manufacturing with full traceability:

- Oxygen plasma for organic clean

- Hydrogen plasma for metal oxide removal

- Cleanroom class 100 (10,000 is standard)

- Inert gas purge for reducing gas chemistry

- Substrate heating and cooling

For more information, contact Surfx at: sales@surfxtechnologies.com or +1 310 558 0770.

#### **STA-10iL Specifications**

**Work area (X \* Y \* Z)** 550 x 760 x 60 mm

**Footprint (W \* D \* H)** 1,000 x 1,500 x 1,550 mm

39.4 x 59.1 x 61.0 inches

#### **Software and OS**

Cloudbreak<sup>™</sup> for rapid program development.

#### Patented plasma technology

Atmospheric argon plasma O<sub>2</sub>, H<sub>2</sub>, N<sub>2</sub> plasma chemistry RF capacitive discharge

www.surfxtechnologies.com

#### **North America**

Surfx Technologies, LLC

Ph: +1 (310) 558-0770

#### Europ

Novel Technology Transfer Gmbl Ph: +49 8134 55700-12 Alex.Wanninger@novel-tec.de

# **ZEISS Xradia Versa X-ray Microscope**

Al-enabled fast, high-resolution 3D X-ray imaging

Submicron 3D visualization of package interconnects and defects

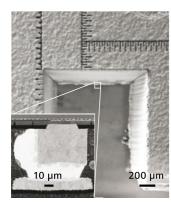

#### ZEISS Crossbeam LaserFIB

From macro to nano in femtoseconds

Targeted sample prep and SEM imaging of microbump in PoP

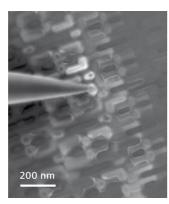

# **ZEISS GeminiSEM** Field-emission SEM

Nanoprobing of unperturbed sample states

Simultaneous sub-nm surface imaging and electrical characterization at 150V

www.zeiss.com/semiconductor-microscopy

## CONTACT

#### **EMPC 2023**

Organised by:

#### **IMAPS UK**

125 High Street Chesterton Cambridge CB4 1NL, UK office@imaps.org.uk

Conference Chair: Anne Vanhoestenberghe

mcc-events.de

**Technical Chair:** Steve Riches

#### PCO

mcc Agentur für Kommunikation GmbH Martina Creutzfeldt. Rahel Dietze & Ajda Omrani Berlin, Germany Phone: +49 30-61 28 86 11 office@empc2023.org